05-STM32F1 - 串行通信SPI

迪丽瓦拉

2025-05-30 15:17:05

0次

SPI

-

STM-SPI作为主机,从机

-

SPI的时钟,最高为Pclk/2,SPI1最高为36Mhz,SPI2最高为18Mhz。

-

SPI的四种模式 CPOL CPHA,数据帧8~16位,LSB,MSB

-

全双工,双向单线,单线

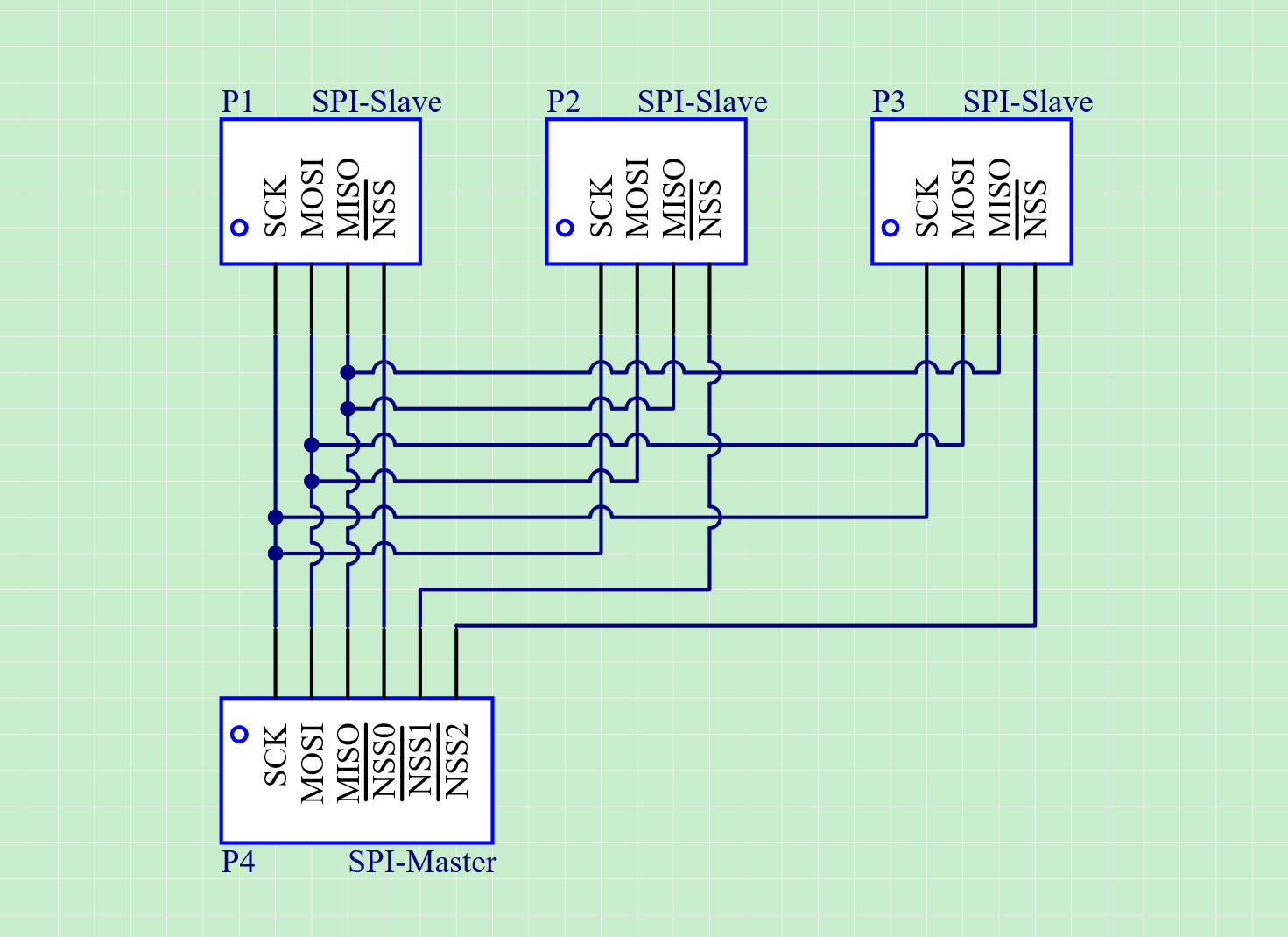

物理层

接口标准

| 序号 | 名称 | 说明 |

|---|---|---|

| 1 | NSS | 片选线,低电平有效 |

| 2 | SCK | 时钟信号线 |

| 3 | MOSI | 主设备输出,从设备输入 |

| 4 | MISO | 主设备输入,从设备输出 |

协议层

起始信号和停止信号

NSS 信号线由高变低,是SPI 通讯的起始信号。NSS 是每个从机各自独占的信号线,当从机在自己的NSS 线检测到起始信号后,就知道自己被主机选中了,开

始准备与主机通讯。在图中的标号处,NSS 信号由低变高,是SPI 通讯的停止信号,表示本次通讯结束,从机的选中状态被取消。

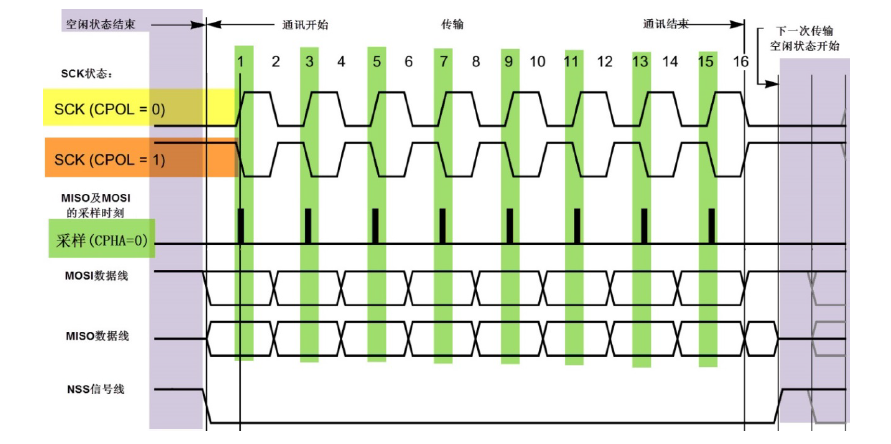

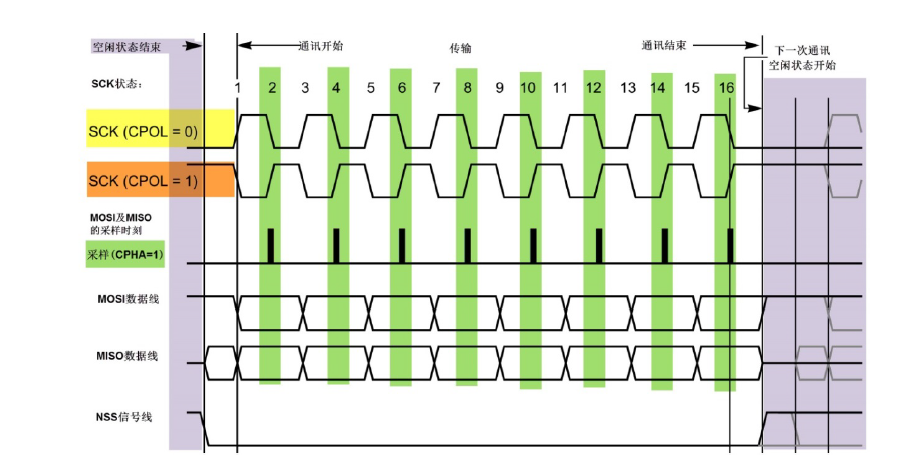

CPOL/CPOH

时钟极性CPOL:SPI 通讯设备处于空闲状态时,SCK 信号线的电平信号(即SPI 通讯开始前,NSS 线为高电平时SCK 的状态)。CPOL=0 时,SCK 在空闲状态时为低电平,CPOL=1 时,SCK 在空闲状态时为高电平,

时钟相位CPHA:数据的采样的时刻。当CPHA=0 时,MOSI 或MISO 数据线上的信号将会在SCK 时钟线的“奇数边沿”被采样。当CPHA=1 时,数据线在SCK 的“偶数边沿”采样。

| SPI模式 | CPOL | CPHA | 空闲时SCK时钟 | 采样时刻 |

|---|---|---|---|---|

| 0 | 0 | 0 | 低电平 | 奇数边沿 |

| 1 | 0 | 1 | 低电平 | 偶数边沿 |

| 2 | 1 | 0 | 高电平 | 奇数边沿 |

| 3 | 1 | 1 | 高电平 | 偶数边沿 |

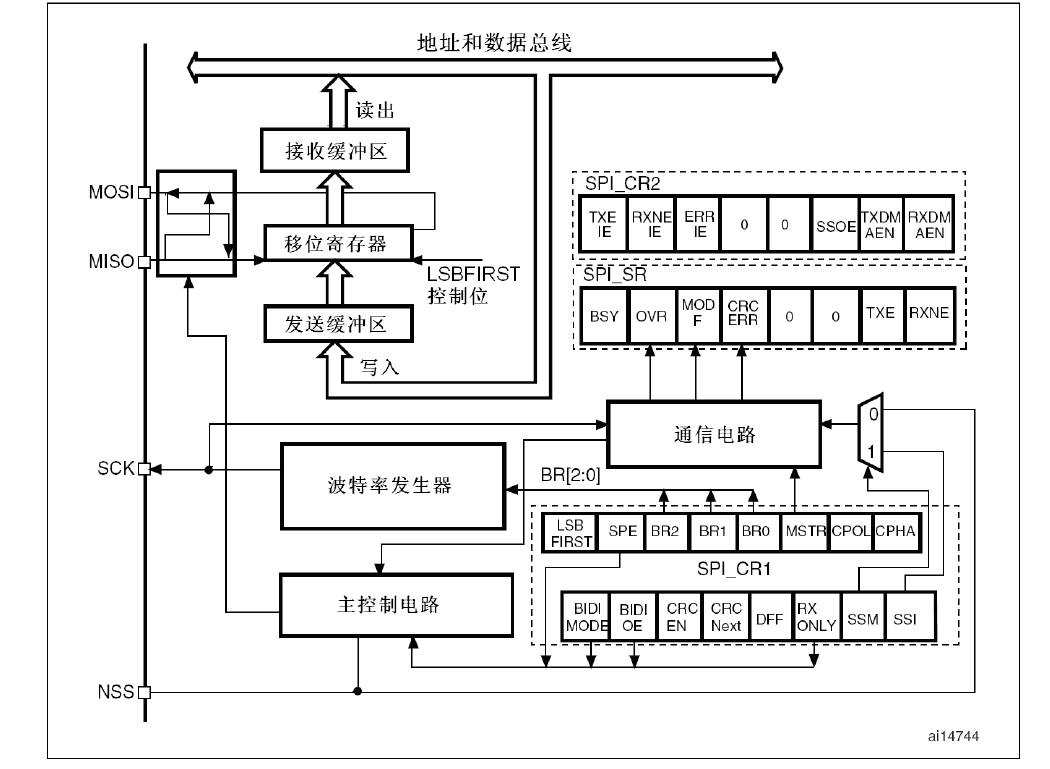

SPI基本结构

- 通讯引脚

- 时钟控制逻辑

- 数据控制逻辑

- 整体控制逻辑

NSS可以使用软件控制,其他引脚使用硬件SPI控制

时钟控制:波特率发生器:BR[2:0],控制SPI的时钟。CR1寄存器

数据控制逻辑:

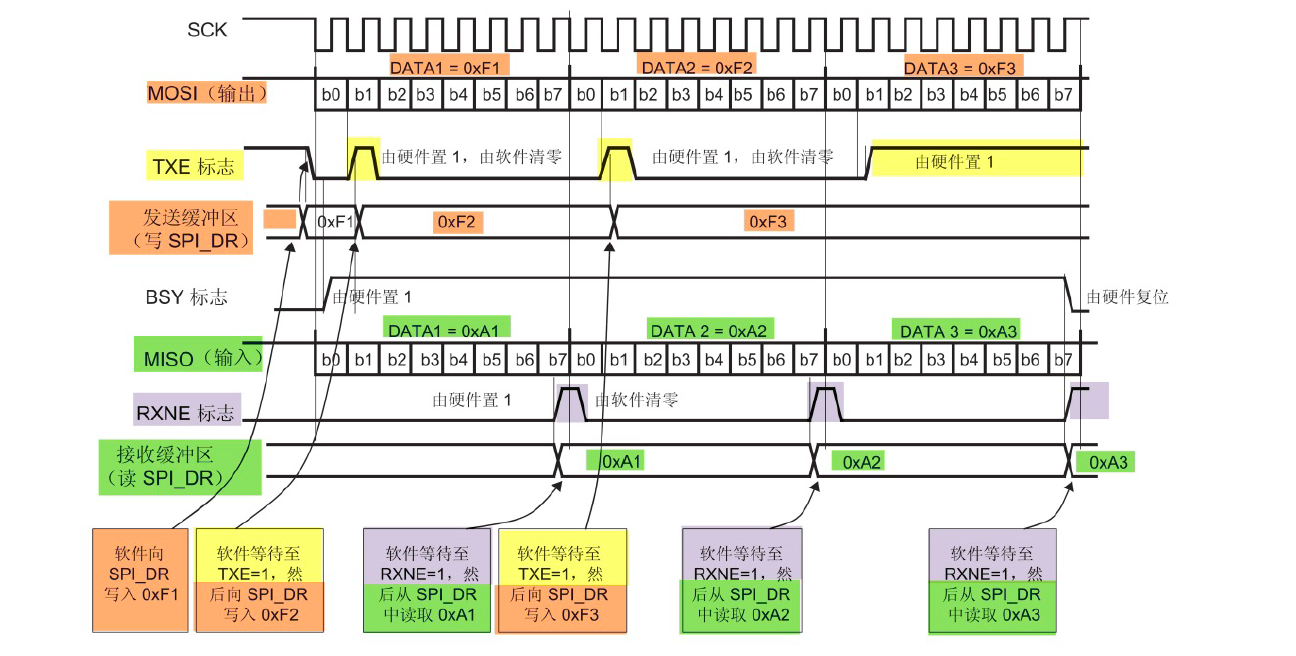

SPI的MOSI及MISO都连接到数据移位寄存器上,数据移位寄存器的数据来源于接收缓冲区及发送缓冲区。

通过写SPI的数据寄存器DR把数据填充到发送缓冲区中。

通过读SPI的数据寄存器DR,可以获取到接收缓冲区中的内容。

其中数据帧长度通过DFF为配置成8位及16位。

模式:配置LSBFIRST位,可选择MSB先行还是LSB先行。

SPI初始化结构体

typedef struct

{uint16_t SPI_Direction; uint16_t SPI_Mode; uint16_t SPI_DataSize; uint16_t SPI_CPOL; uint16_t SPI_CPHA; uint16_t SPI_NSS; uint16_t SPI_BaudRatePrescaler; uint16_t SPI_FirstBit; uint16_t SPI_CRCPolynomial;

}SPI_InitTypeDef;

编程要点

下一篇:RHCE第二天

相关内容

热门资讯

linux入门---制作进度条

了解缓冲区 我们首先来看看下面的操作: 我们首先创建了一个文件并在这个文件里面添加了...

C++ 机房预约系统(六):学...

8、 学生模块 8.1 学生子菜单、登录和注销 实现步骤: 在Student.cpp的...

A.机器学习入门算法(三):基...

机器学习算法(三):K近邻(k-nearest neigh...

数字温湿度传感器DHT11模块...

模块实例https://blog.csdn.net/qq_38393591/article/deta...

有限元三角形单元的等效节点力

文章目录前言一、重新复习一下有限元三角形单元的理论1、三角形单元的形函数(Nÿ...

Redis 所有支持的数据结构...

Redis 是一种开源的基于键值对存储的 NoSQL 数据库,支持多种数据结构。以下是...

win下pytorch安装—c...

安装目录一、cuda安装1.1、cuda版本选择1.2、下载安装二、cudnn安装三、pytorch...

MySQL基础-多表查询

文章目录MySQL基础-多表查询一、案例及引入1、基础概念2、笛卡尔积的理解二、多表查询的分类1、等...

keil调试专题篇

调试的前提是需要连接调试器比如STLINK。 然后点击菜单或者快捷图标均可进入调试模式。 如果前面...

MATLAB | 全网最详细网...

一篇超超超长,超超超全面网络图绘制教程,本篇基本能讲清楚所有绘制要点&#...

IHome主页 - 让你的浏览...

随着互联网的发展,人们越来越离不开浏览器了。每天上班、学习、娱乐,浏览器...

TCP 协议

一、TCP 协议概念 TCP即传输控制协议(Transmission Control ...

营业执照的经营范围有哪些

营业执照的经营范围有哪些 经营范围是指企业可以从事的生产经营与服务项目,是进行公司注册...

C++ 可变体(variant...

一、可变体(variant) 基础用法 Union的问题: 无法知道当前使用的类型是什...

血压计语音芯片,电子医疗设备声...

语音电子血压计是带有语音提示功能的电子血压计,测量前至测量结果全程语音播报...

MySQL OCP888题解0...

文章目录1、原题1.1、英文原题1.2、答案2、题目解析2.1、题干解析2.2、选项解析3、知识点3...

【2023-Pytorch-检...

(肆十二想说的一些话)Yolo这个系列我们已经更新了大概一年的时间,现在基本的流程也走走通了,包含数...

实战项目:保险行业用户分类

这里写目录标题1、项目介绍1.1 行业背景1.2 数据介绍2、代码实现导入数据探索数据处理列标签名异...

记录--我在前端干工地(thr...

这里给大家分享我在网上总结出来的一些知识,希望对大家有所帮助 前段时间接触了Th...

43 openEuler搭建A...

文章目录43 openEuler搭建Apache服务器-配置文件说明和管理模块43.1 配置文件说明...